Pipelining

To

understand how pipelining works

How Pipelining Works

Pipelined Laundry

Pipelining, a standard feature in RISC processors, is much like an assembly line. Because the processor works on different steps of the instruction at the same time, more instructions can be executed in a shorter period of time.

A useful method of demonstrating this is the laundry analogy. Let's say that there are four loads of dirty laundry that need to be washed, dried, and folded. We could put the the first load in the washer for 30 minutes, dry it for 40 minutes, and then take 20 minutes to fold the clothes. Then pick up the second load and wash, dry, and fold, and repeat for the third and fourth loads. Supposing we started at 6 PM and worked as efficiently as possible, we would still be doing laundry until midnight.

To

study how pipelining can be used to build

fast processors

Pipelining

and parallelism

are 2 methods used to achieve concurrency.

—Pipelining

increases concurrency by dividing a computation into a number of steps.

—Parallelism

is the use of multiple resources to increase concurrency.

Pipelining is a key implementation technique used to build fast processors that can be seen in RISC architecture. It allows the execution of multiple instructions to overlap in time.

In a non-pipelined processing, by contrast, the next data/instruction is processed after the entire processing of the previous data/instruction is complete.

There are TWO type of laundry in pipelined:

Sequential Laundry

However, a smarter approach to the problem would be to put the second load of dirty laundry into the washer after the first was already clean and whirling happily in the dryer. Then, while the first load was being folded, the second load would dry, and a third load could be added to the pipeline of laundry. Using this method, the laundry would be finished by 9:30.

If you glance back at the diagram of the laundry pipeline, you'll notice that although the washer finishes in half an hour, the dryer takes an extra ten minutes, and thus the wet clothes must wait ten minutes for the dryer to free up. Thus, the length of the pipeline is dependent on the length of the longest step. Because RISC instructions are simpler than those used in pre-RISC processors (now called CISC, or Complex Instruction Set Computer), they are more conducive to pipelining. While CISC instructions varied in length, RISC instructions are all the same length and can be fetched in a single operation. Ideally, each of the stages in a RISC processor pipeline should take 1 clock cycle so that the processor finishes an instruction each clock cycle and averages one cycle per instruction (CPI).

In a

non-pipelined CPU, instructions are performed “one at a time”.ie.

before an instruction is

begun, the preceding instruction is completed.

To

implement instruction pipelining, desirable features of

(instruction set) IS:

—all

instructions same length

—registers

specified in same place in instruction

—memory

operands only in loads or stores, i.e. RISC

But,

it is not always the case in reality

To be

aware of the limitations of pipelining

3

types of hazards:

-Resource hazards :

HW cannot support this combination of instructions (single person to fold and

put clothes away, washer-drier)

-Data hazards:

Instruction depends on result of prior instruction still in the pipeline

-Data

dependencies example

A

= B + C

D

= E + A

C

= G x H

-Control hazards:

Caused by delay between the fetching of instructions and decisions about

changes in control flow (branches and jumps).

To

understand characteristics and design of RISC

RISC:

Reduced Instruction Set Computers

•Major

advances in computer :

—The

family concept

–Separates

architecture from implementation

—Microprogrammed

control unit

—Cache

memory

—Solid

State RAM

—Microprocessors

—Pipelining

–Introduces

parallelism into fetch execute cycle

—Multiple

processors

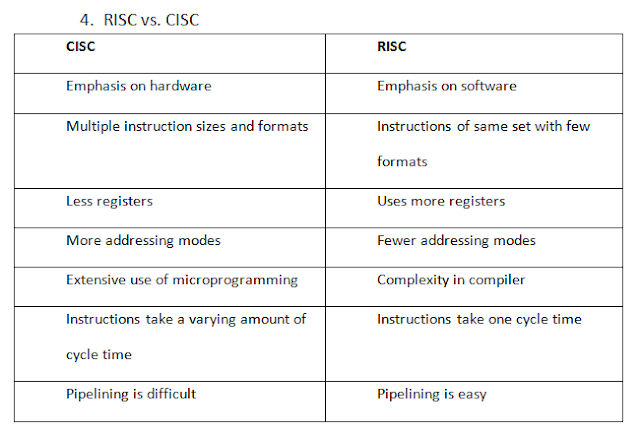

To

contrast CISC and RISC

CISC

and RISC

•Key

features of CISC:

—Large

number of predefined instructions making high level programming languages easy

to design and implement.

—Supports

microprogramming to simplify computer architecture

—

•Key

features of RISC

—Limited

and simple instruction set

—Large

number of general purpose registers or use of compiler technology to optimize

register use.

—Emphasis

on optimizing the instruction pipeline

0 comments: